## Parallel Computing

Timing and Debugging

Wrap-Up of CUDA

Matrix Multiplication

Histogram

(from Jason Sanders' book; see our webpage link)

Note: Jason Sanders uses HANDLE\_ERROR instead of our ERR\_CHECK

(.../00\_error/cuda\_error\_check.h)

#### Before we start...

#### **Some nice ideas:**

/home/Tit4/lecture60/gpu-course/00\_error/

(ERR\_CHECK instead of HANDLE\_ERROR)

/home/Tit4/lecture60/gpu-course/4\_dot/dot-special-new.cu (dynamic vector size allocation in kernel through <<<n,m,size>>>)

### Recap of 6: dot\_perfect.cu:

Fat Threads! New variable gridDim.x!

Use of gridDim.x \* blockDim.x to get size of grid,

Relation to <<<n,m>> in kernel launch

Block Reduction on Host instead of AtomicAdd!

Also used for histogram later.

Note nice profiling nvprof used in 7\_matmul/gpu\_script.sh https://docs.nvidia.com/cuda/profiler-users-quide/index.html

#### This Timing API is used in 8\_histo/histo.cu!

### Timing with CUDA Event API

```

int main ()

CUDA Event API Timer are,

cudaEvent_t start, stop;

float time;

OS independent

cudaEventCreate (&start);

- High resolution

cudaEventCreate (&stop);

Useful for timing asynchronous calls

cudaEventRecord (start, 0);

someKernel <<<grids, blocks, 0, 0>>> (...);

cudaEventRecord (stop, 0);

cudaEventSynchronize (stop); - Ensures kernel execution has completed

cudaEventElapsedTime (&time, start, stop);

cudaEventDestroy (start);

cudaEventDestroy (stop);

printf ("Elapsed time %f sec\n", time*.001);

return 1;

Standard CPU timers will not measure the

}

timing information of the device.

```

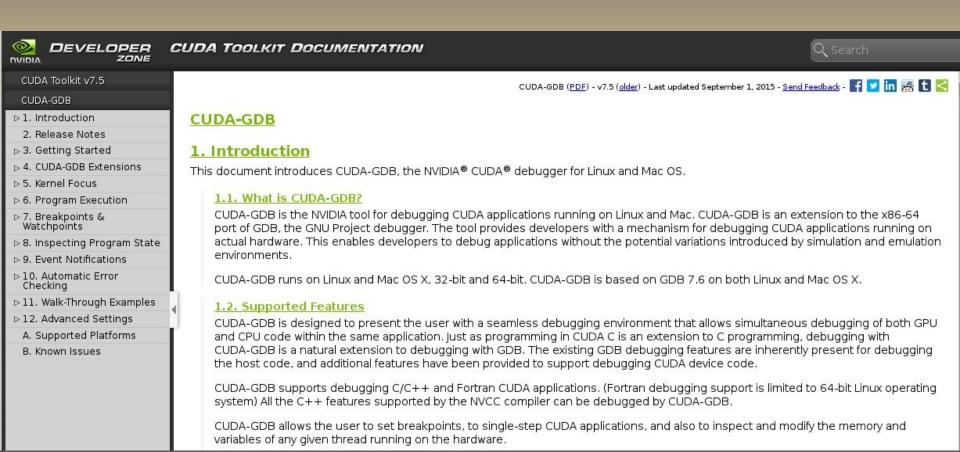

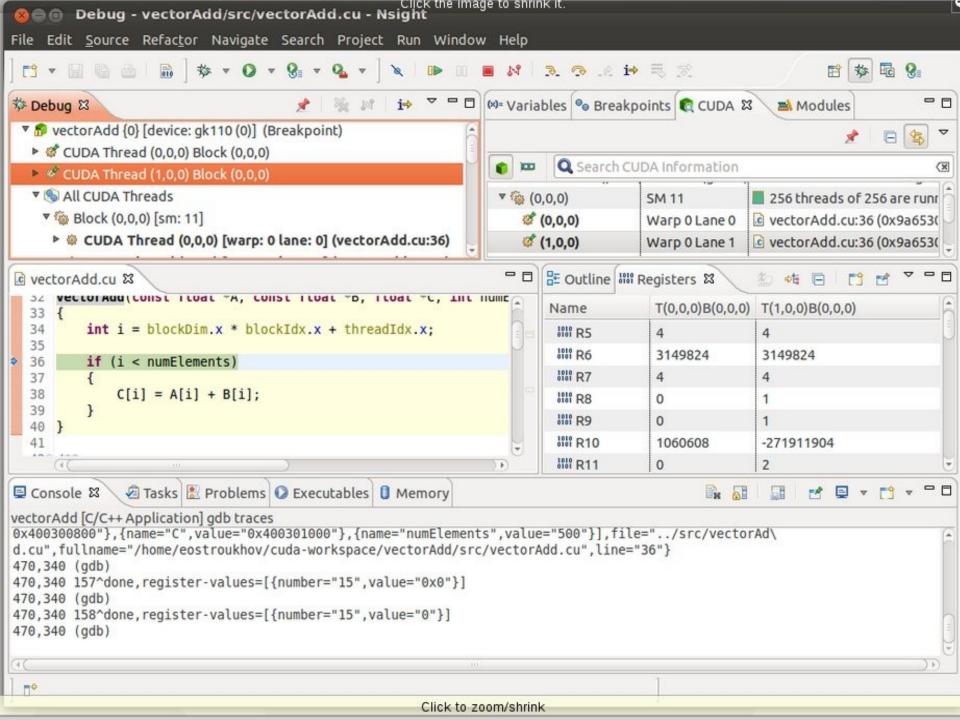

#### **CUDA – GNU Debugger – CUDA-gdb**

http://docs.nvidia.com/cuda/cuda-gdb/index.html

### Wrapping Up 1

### Exercises (CUDA Lectures in afternoon)

- 0. hello, device- first kernel call, hello world, GPU properties

- 1. add vector addition using one thread in one block only

- 2. add-index vector addition using blocks in parallel, one thread per block only.

- 3. add-parallel vector addition using all blocks and threads in parallel

- 4. dot scalar product using shared memory of one block only for reduction

- 5. dot-full scalar product using shared memory and atomic add across blocks

- 6. dot-perfect scalar product; fat threads and final reduction on host.

- 8. histo histogram using fat threads and atomic add on shared and global memory, timing

- 7. matmul matrix multiplication with tiled access shared memory (expect Friday)

### Wrapping Up 2

#### **Elements of CUDA C learnt:**

```

threadId.x, blockId.x, blockDim.x, gridDim.x

(threadId.y, blockId.y, blockdim.y, gridDim.y

shared

cudaMalloc / cudaFree

cudaMemcpy / cudaMemset

cudaGetDeviceProperties

cudaEventCreate, cudaEventRecord,

cudaEventSynchronize, cudaEventElapsedTime,

cudaEventDestroy

AtomicAdd

```

Threads, Blocks

(matmul coming with 2D grids)

kernel calls

kernel call with dyn. alloc. size

dim3 variable type (matmul)

shared memory on GPU manage global memory of GPU copy/set to or from memory get device properties in program

CUDA profiling atomic functions

### Wrapping Up 3

#### What we have not yet learnt...

\_\_constant\_\_ \_\_device\_\_ Intrinsic Functions ( \_\_device\_\_ type)

IMI#group CUDA MATH SINGLI

functions host to host

constant memory on GPU

functions device to device

\_\_host\_\_

More atomic functions

cudaBindTexture

fat threads for 2D and 3D stencils

cudaStreamCreate, cudaStreamDestroy

<<<n,m,size,s>>>

using Tensor Cores

using texture memory thread coalescence opt. working with CUDA streams kernel call with streams s

...

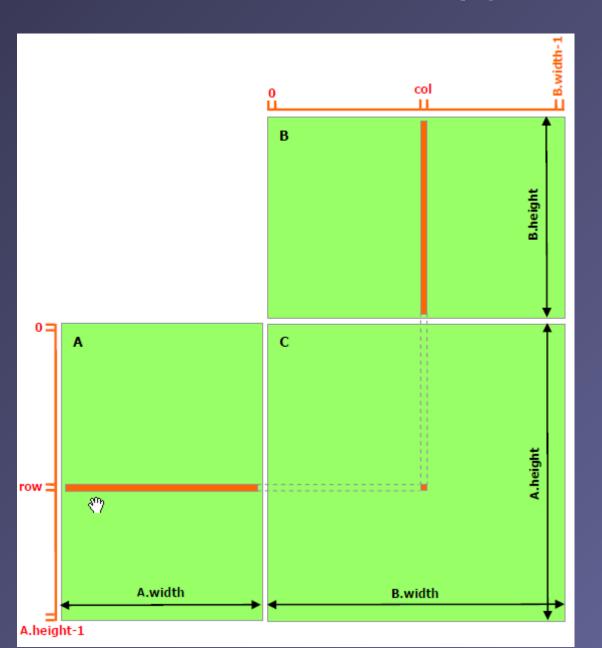

## Matrix Multiply and Histogram

Matrix Multiply: Inspired by Lecture of Wen-mei Hwu

http://whtresearch.sourceforge.net/example.html

On kepler: 7\_matmul/

### Histo: Chapter in Book of Jason Sanders

https://wwwstaff.ari.uni-heidelberg.de/spurzem/lehre/WS21/cuda/files/cuda-histograms.pdf

(Link on our webpage)

On kepler: 8\_histo/

histo.cu (atomic on both shared and global memory)

histo-no-atomic.cu (atomic only on global memory)

### **Matrix Intuitive Multiply**

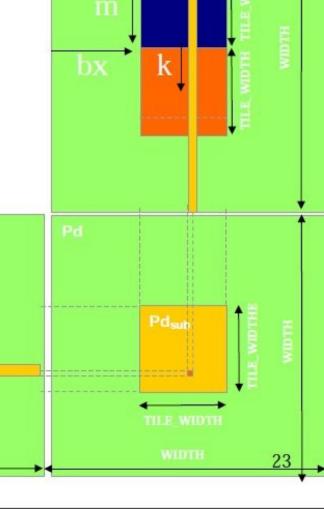

# Tiled Multiply

- Each block computes one square sub-matrix Pd<sub>sub</sub> of size TILE\_WIDTH

- Each thread computes one element of Pd<sub>sub</sub>

©Wen-mei W. Hwu and David Kirk/NVIDIA, Berkeley, January 24-25, 2011

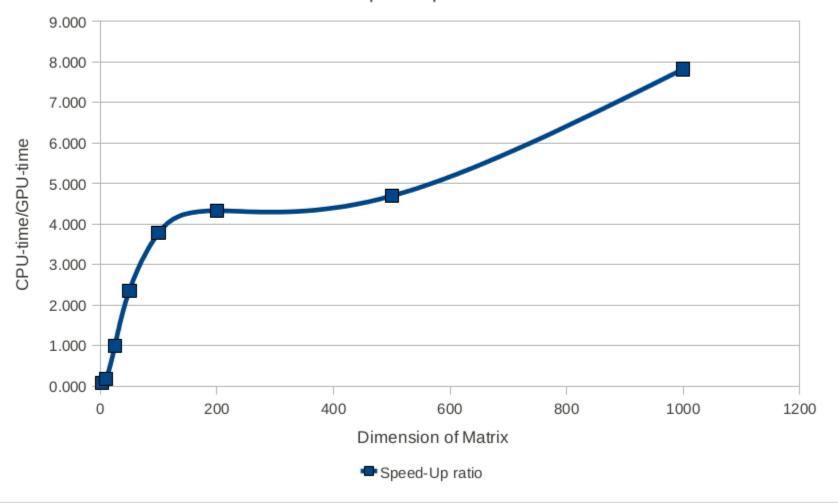

Speed-Up Ratio

GPU speed-up over CPU

### Final Remarks

#### **Important Note:**

If you do some NBODY research in the future, please contact us (tutors or lecturer); do not use the course code for research it is not fully performant in some respects (openMP).

#### Remember for course certificate:

- \* Output files of small experiments on your lecture account (0\_hello, 1\_add, ..., 7-matmul, 8-histo)

- \* Return two plots, one data file, and a few comments to your tutors Deadline? Agree with tutors, no strict deadline, but please NOT one day before you need the certificate! Outputs of the 8 Nbody runs on your lecture account.

- \* Notice: Student Queues will close Sunday, Mar 6, 23:59 (latest).

You can run later, but contact me please spurzem@ari.uni-heidelberg.de

### Additional deeper material:

Lectures by Prof. Wen-Mei Hwu Chicago in Berkeley 2012 and Beijing 2013, see <a href="http://iccs.lbl.gov/workshops/tutorials.html">http://iccs.lbl.gov/workshops/tutorials.html</a> (down on page links to all lecture files, also available on request from spurzem@nao.cas.cn)

Lecture1: Computational thinking

Lecture2: Parallelism Scalability

Lecture3: Blocking Tiling

Lecture4: Coarsening Tiling

Lecture5: Data Optimization

Lecture6: Input Binning

Lecture7: Input Compaction

Lecture8: Privatization

See also:

http://freevideolectures.com/Course/2880/Advanced-algorithmic-techniques-for-GPUs/1

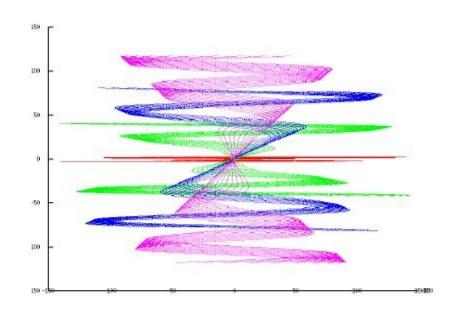

# Massive Parallelism - Regularity

©Wen-mei W. Hwu and David KIR/NVIDIA, Berkeley, January 24-25, 2011

### Main Hurdles to Overcome

- Serialization due to conflicting use of critical resources

- Over subscription of Global Memory bandwidth

# Computational Thinking Skills

- The ability to translate/formulate domain problems into computational models that can be solved efficiently by available computing resources

- Understanding the relationship between the domain problem and the computational models

- Understanding the strength and limitations of the computing devices

- Defining problems and models to enable efficient computational solutions

### DATA ACCESS CONFLICTS

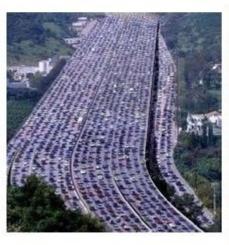

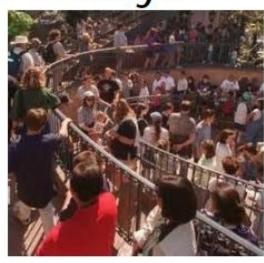

# Conflicting Data Accesses Cause Serialization and Delays

Massively parallel execution cannot afford serialization

Contentions in accessing critical data causes serialization

# A Simple Example

- A naïve inner product algorithm of two vectors of one million elements each

- All multiplications can be done in time unit (parallel)

- Additions to a single accumulator in one million time units (serial)

23

### How much can conflicts hurt?

- Amdahl's Law

- If fraction X of a computation is serialized, the speedup can not be more than 1/(1-X)

- In the previous example, X = 50%

- Half the calculations are serialized

- No more than 2X speedup, no matter how many computing cores are used

# GLOBAL MEMORY BANDWIDTH

# Global Memory Bandwidth

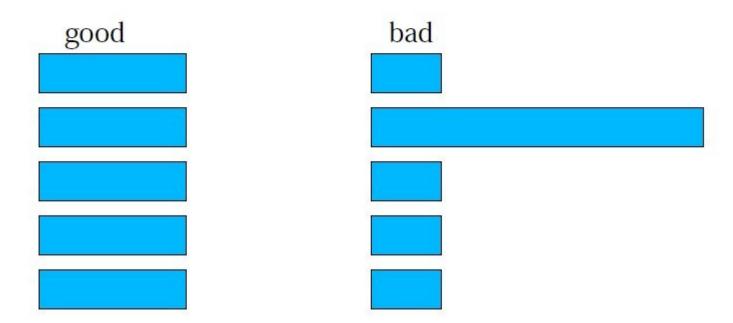

#### Ideal

#### Reality

©Wen-mei W. Hwu and David Kirk/NVIDIA, Berkeley, January 24-25, 2011

# Global Memory Bandwidth

- Many-core processors have limited off-chip memory access bandwidth compared to peak compute throughput

- Fermi

- 1 TFLOPS SPFP peak throughput

- 0.5 TFLOPS DPFP peak throughput

- 144 GB/s peak off-chip memory access bandwidth

- 36 G SPFP operands per second

- 18 G DPFP operands per second

- To achieve peak throughput, a program must perform 1,000/36 = ~28 SPFP (14 DPFP) arithmetic operations for each operand value fetched from off-chip memory 27

Berkeley, January 24-25, 2011

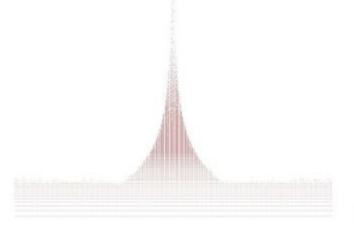

### LOAD BALANCE

### Load Balance

The total amount of time to complete a parallel job is limited by the thread that takes the longest to finish

### How bad can it be?

- Assume that a job takes 100 units of time for one person to finish

- If we break up the job into 10 parts of 10 units each and have fo10 people to do it in parallel, we can get a 10X speedup

- If we break up the job into 50, 10, 5, 5, 5, 5, 5, 5, 5, 5, 5, 5 units, the same 10 people will take 50 units to finish, with 9 of them idling for most of the time. We will get no more than 2X speedup.

### How does imbalance come about?

- Non-uniform data distributions

- Highly concentrated spatial data areas

- Astronomy, medical imaging, computer vision, rendering, ...

- If each thread processes the input data of a given spatial volume unit, some will do a lot more work than others

# Eight Algorithmic Techniques (so far)

| Technique                    | Contention | Bandwidth | Locality | Efficiency | Load Imbalance | CPU Leveraging |

|------------------------------|------------|-----------|----------|------------|----------------|----------------|

| Tiling                       |            | X         | X        |            |                |                |

| Privatization                | X          |           | X        |            |                |                |

| Regularization               |            | 10        |          | X          | X              | X              |

| Compaction                   |            | X         |          |            |                |                |

| Binning                      |            | X         | X        | X          |                | X              |

| Data Layout Transformation   | X          |           | X        |            |                |                |

| Thread Coarsening            | X          | X         | X        | X          |                |                |

| Scatter to Gather Conversion | X          |           |          |            |                |                |

http://courses.engr.illinois.edu/ece598/hk/

### You can do it.

- Computational thinking is not as hard as you may think it is.

- Most techniques have been explained, if at all, at the level of computer experts.

- The purpose of the course is to make them accessible to domain scientists and engineers.

# **ANY MORE QUESTIONS?**